Timing Arc is defined as the path traversed by a Signal from the Input Pin of a Cell to its Output Pin. For a Cell, there can be more than one Timing Arc and by the information of different Timing Arcs that exists for a Cell, we can calculate the delay for each path that will help in Timing Analysis and Optimization.

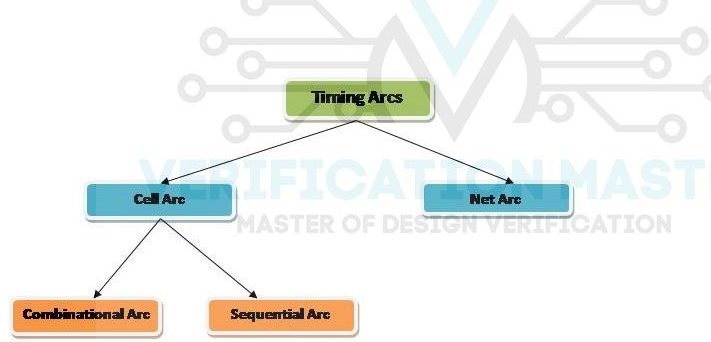

Types of Timing Arcs

Fig. 1: Types of Timing Arc

Cell Arcs

It is defined as a path traversed by a signal from the Input/Source pin of a cell to the output/sink pin of the cell. It is of two types:

- Combinational Arcs

The path is traversed by a Signal from Input Pin to Output Pin of a combination cell.

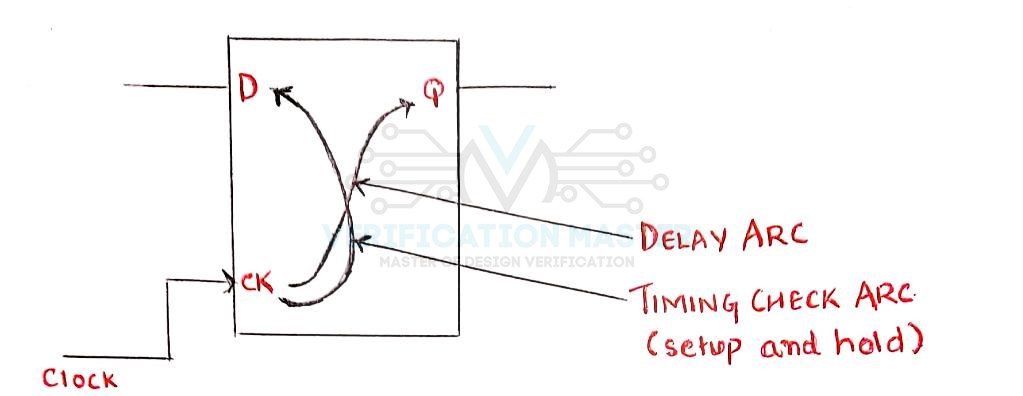

- Sequential Arcs

The path is traversed by a Signal from Clock Pin to the Output Pin or Clock Pin to the Input Pin of a sequential cell. Timing Check Arcs i.e. Setup Check and Hold Check exists between clock pin and input pin of a sequential cell. Between clock pin and output pin, sequential delay arc exists. Refer Fig.2

Fig. 2: Sequential Delay Arc

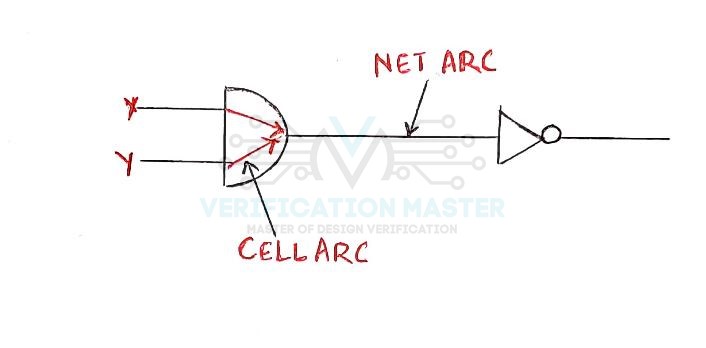

Net Arcs

The arc between the output pin of a cell and input pin of another cell is known as Net Arcs or Net Arc is the Arc between driver pin and load pin of a particular Net. Net Arcs constitute to delay in the timing path this is the reason why net arcs are always Delay Timing Arcs. Refer Fig.3

Fig. 3: Net Arc

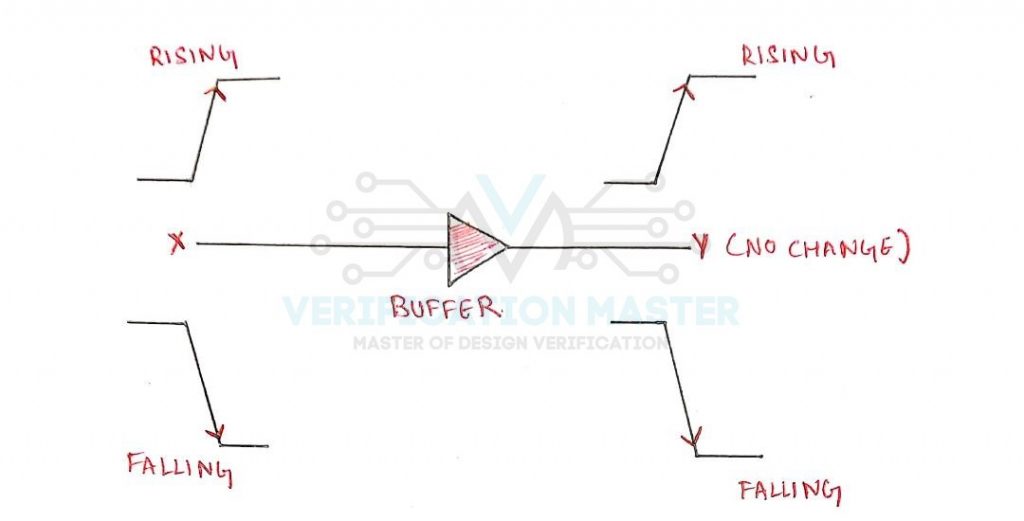

Unateness

When an Input is applied at the input pin there is a change in value at the Output. Unateness is defined as the sense of change in output w.r.t the input applied and the time it takes to reflect that change. Unateness is of three types:

- Positive Unate

When the input goes from low-high it will cause the output to change from low-high and vice versa. Examples are Buffer, AND Gate and OR Gate

Fig. 4: Positive Unate

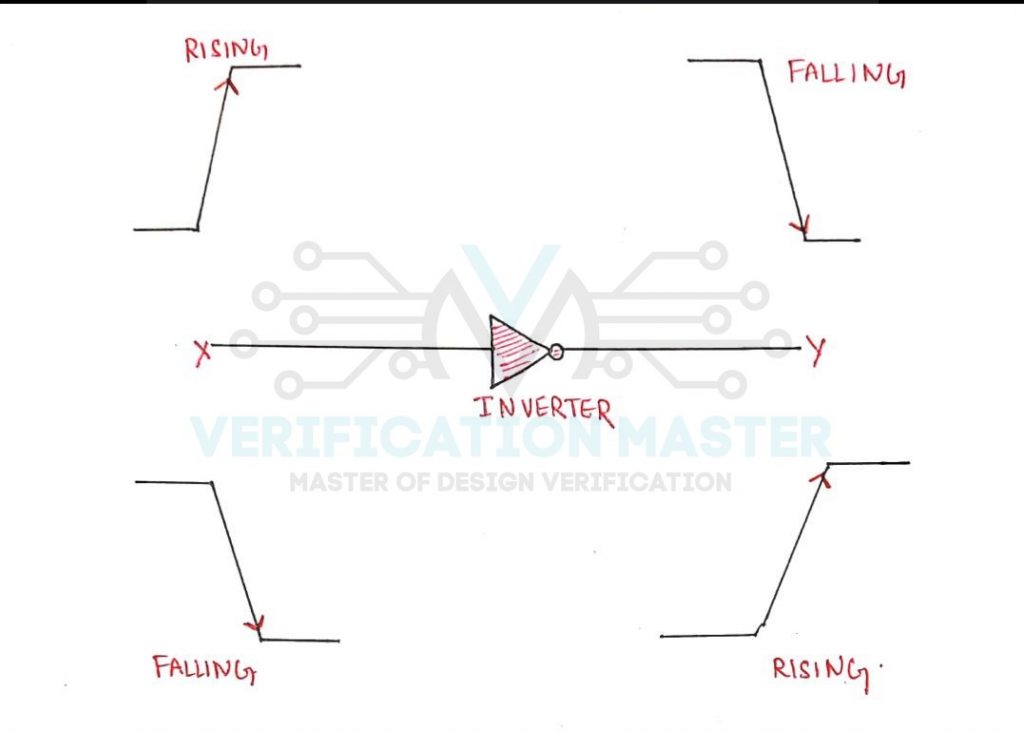

- Negative Unate

When the input goes from low-high it will cause the output to change from high-low and vice-versa. Examples are NAND Gate, NOR Gate, and Inverter

Fig. 5: Negative Unate

- Non-Unate

The output transition does not depend on one input, but also depends on other inputs applied. Examples are XOR Gate and XNOR Gate.

- Significance of Unateness

Unateness only tells that how the output is sensitive to the applied input. Also, as cell delay depends upon the input slew and output load so somewhere if the input slew will be high then in that case signal will take time to reach the output.

Now, from this blog you can answer the below set of questions:

-

- Q1) What is a timing arc?

- Q2) Explain types of timing arcs.

- Q3) What is Unateness?

- Q4) Explain types of Unateness.