Placement is the stage where the Standard Cells are placed in the design. Previously in floorplan Macro placement is done.

This stage is the process of giving a suitable physical location for all cells in the block. The tool only determines the location of each standard cell on the die based on algorithms used internally.

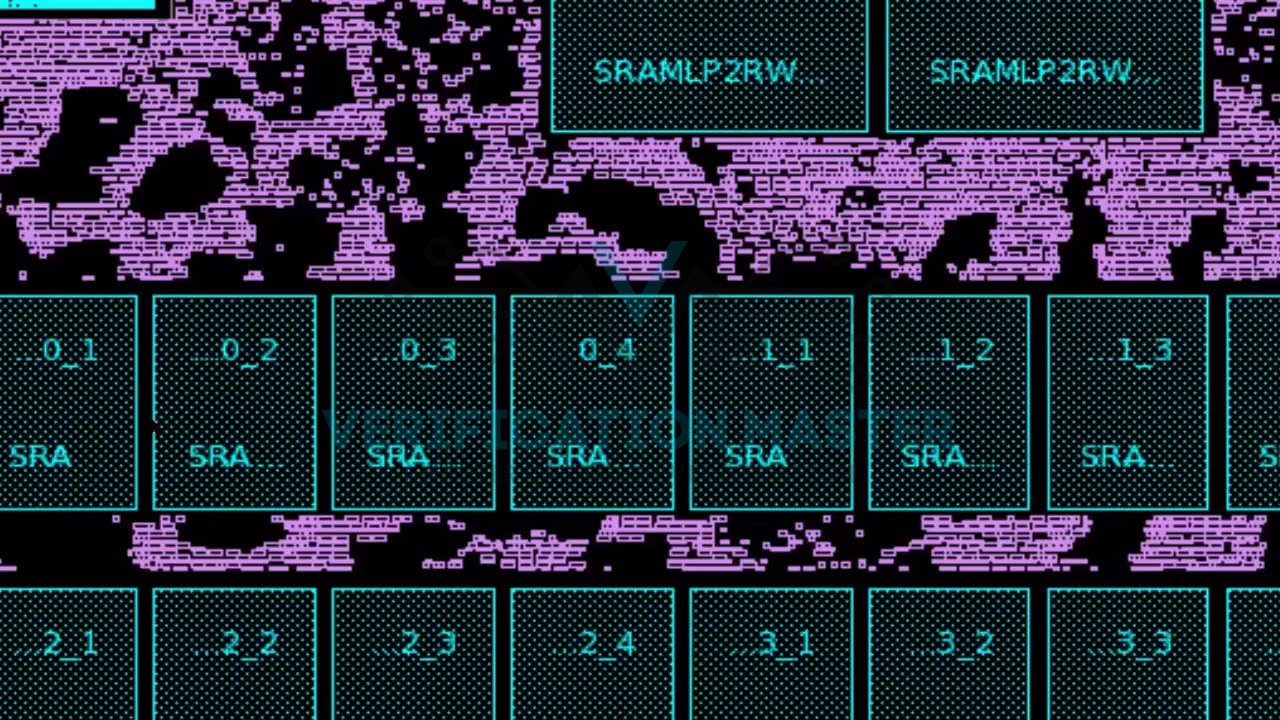

Placement View

The above picture represents Standard Cells and Macro Placement in design. Green Colour represents Macros and Purple represents Standard Cells.

Based on the timing critical or congestion critical design the following are preferred. Mostly at the second iteration, Physical Design Engineer will know when to choose what(either timing or congestion driven).

During the first iteration, one can exactly know if the design is timing critical or congestion critical. Now based on this, the designer decides to choose what kind of placement has to be done.

Timing-driven placement is designed to target wires on timing critical paths. Making some targeted nets shorter during the placement stage might sacrifice the wire lengths of other nets that are connected through common cells. Though the delay on critical paths decreases, other paths have higher chances to become critical. Therefore, has it to be performed in a very careful and balanced way.

icc2_shell> create_placement -timing_driven

Congestion occurs if the number of routing tracks available is less when compared to the required routing tracks.Pin-density-based methods, and routing-estimation-based methods are mainly targeted at Congestion-driven placement. Global routers are often used to drive.

A region with the highest Pin-Density is identified through a Congestion Map.

Through G-Cells estimation is done and Congestion is resolved.

icc2_shell> create_placement -congestion

In Short,