From Setup and Hold time Equation blog, you get a clear understanding of Setup Time and Hold Time. Now, the question that can arise is that from where this Setup Time and Hold Time concept arises. Every Flip Flop has its Setup requirement and Hold requirement for the proper Launch and Capture of Data. So how this property is defined for flip-flops.

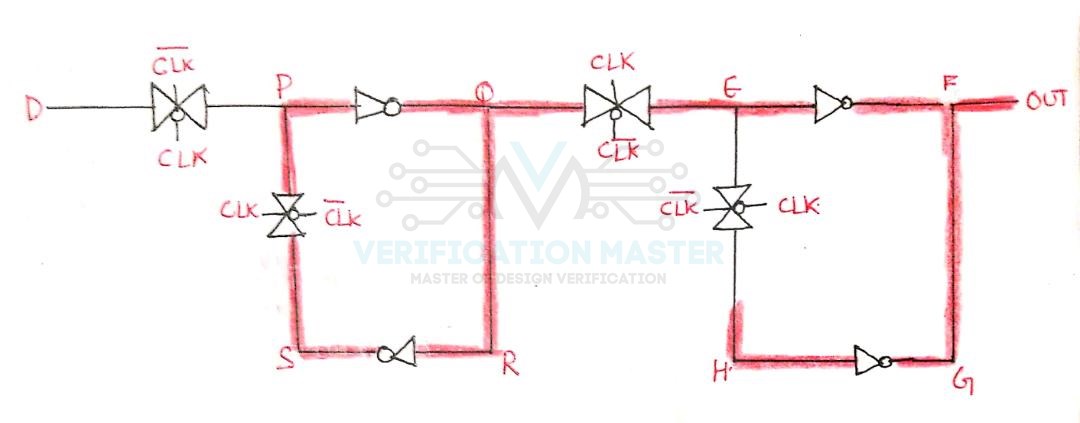

Fig. 1: D = 0 and Negative Clock Edge

From Fig.1 Initially consider D=0 and Negative Clock Edge. The path followed by input is D->P->Q->R->S and at S value is 0. Do not consider the RHS circuit for now

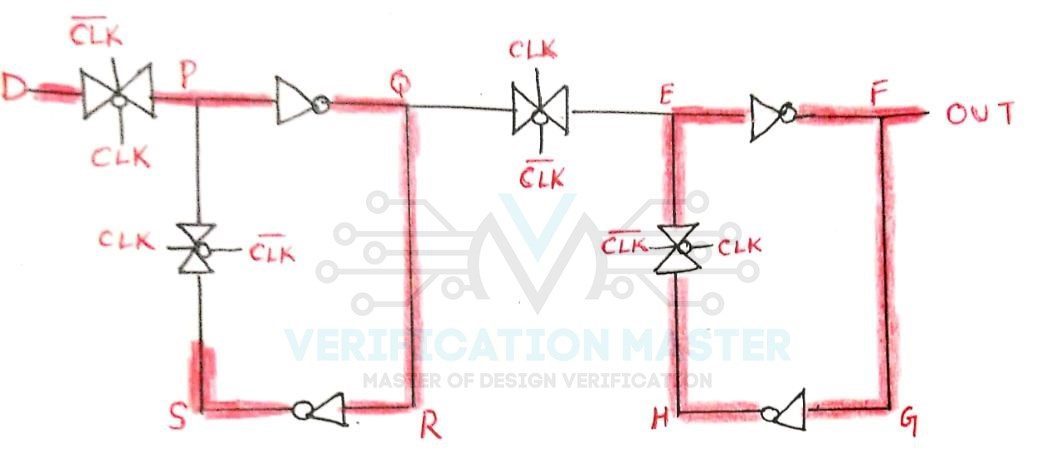

Fig. 2: Out = 0 and Postive Clock Edge

From Fig.2 when Positive Edge arrives the LHS side latches 1 following the path S->P->Q->E->F->OUT which gives 0 at the output OUT. As output comes at a positive edge so it is positive edge-triggered D Flip-Flop

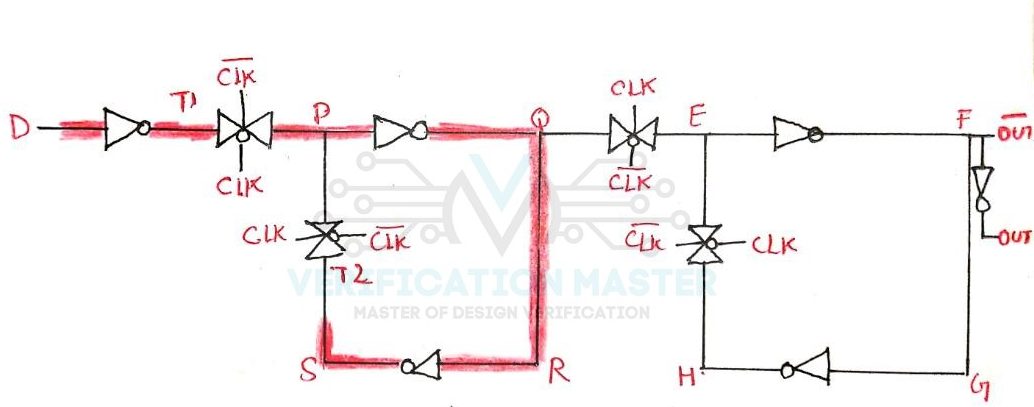

Fig. 3: D = 0 and Negative Clock Edge

From Fig.3 with negative clock edge. The latch circuit on RHS is in active mode but nothing is changed at the output OUT. Whenever input changes it is reflected at S and change in output OUT will be reflected only at the Positive Edge.

Setup Time Concept

Fig. 4: D = 0 and Negative Clock Edge

From Fig. 4 When D=0 and Clk are at the negative edge. D is reflected at S through the path D->P->Q->R->S. Where D=0, P=1, Q=0 and S=1. So, the path traversed through D->P->Q->R->S will take some delay which is referred to as Setup Time of the Flip-Flop. When Positive Edge of Clock comes T1 turns OFF and T2 turns ON producing the output OUT = 0 which is the same as the input (working of D Flip-Flop).

Hold Time Concept

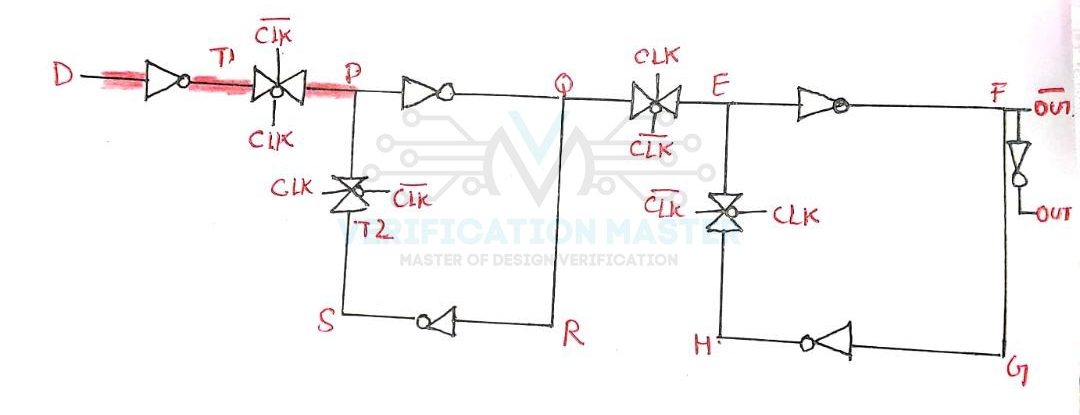

Fig. 5: Hold Time Concept

From Fig.5 When T1 switches between Clk and Clk Bar, due to ramping of the clock signal (clock signal passing through buffers and inverters) there is a definite amount of Delay introduced in the switching activity from high to low and low to high. In the meantime Data present at D should remain stable to produce a stable value at P which will, in turn, give a stable value at output OUT. So the time taken will give rise to the hold time of the Flip-Flop.

So from this Blog, you can answer the below set of questions:

- Q1) How Setup and Hold Time Arises in a Flip-Flop?

- Q2) Explain Latch Based Circuit for the Setup and Hold Time.