Generally, the Data Launched from Launch Flop takes a Single Clock Cycle to reach the Capture Flop. But, there are some cases when the Data is not able to travel from Launch to Capture Flop in Single Clock Cycle. So, in short, When the Data takes more than One Clock Cycle to travel from Launch Flop to Capture Flop it is known as Multicycle Path. Multicycle Path is implemented by Gating the Clock Path or Gating the Data Path.

Examples of MultiCycle Path

Case 1: Launch Flop at Slow Clock and Capture Flop at Faster Clock

Suppose Clock of Capture Flop is three times faster than Clock of Launch Flop. It means Capture Flop will receive Data once in the duration of three Clock Cycles. It will lead to unnecessary wastage of Clock Cycles and Power Dissipation also. To overcome this Multicycle Path can be introduced architecturally by which the Data will be received after a gap of two Clock Cycles

Case 2: Large Data Path Delay

There are some cases in which Data Path Delay is too large that the Launching and Capturing of Data cannot be done in a Single Clock Cycle. So to overcome this a Multicycle Path is defined for such cases. The rest of the Design will work on a Single Clock Cycle.

Setup and Hold Check in Multicycle Path

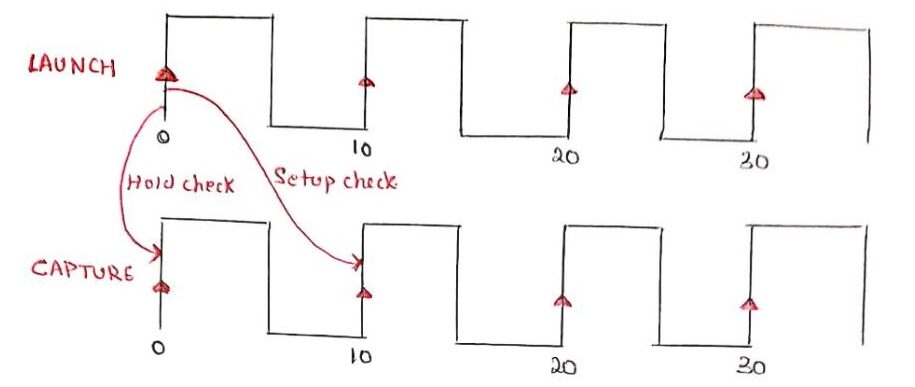

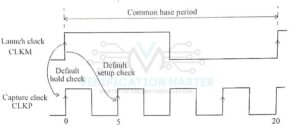

Fig. 1: Setup and Hold Check in Normal Case

This is the Default Setup and Hold Check case. Setup Check will take place on the next Active Edge of Clock and Hold Check will take place one Edge before Setup Check i.e. on the Current Active Clock Edge.

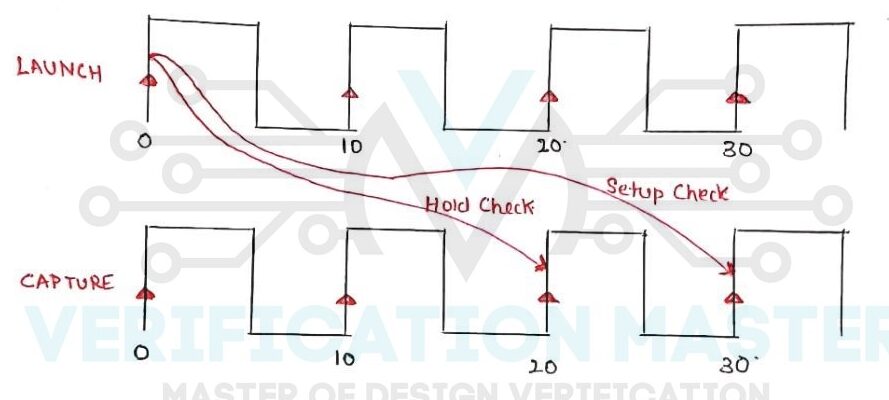

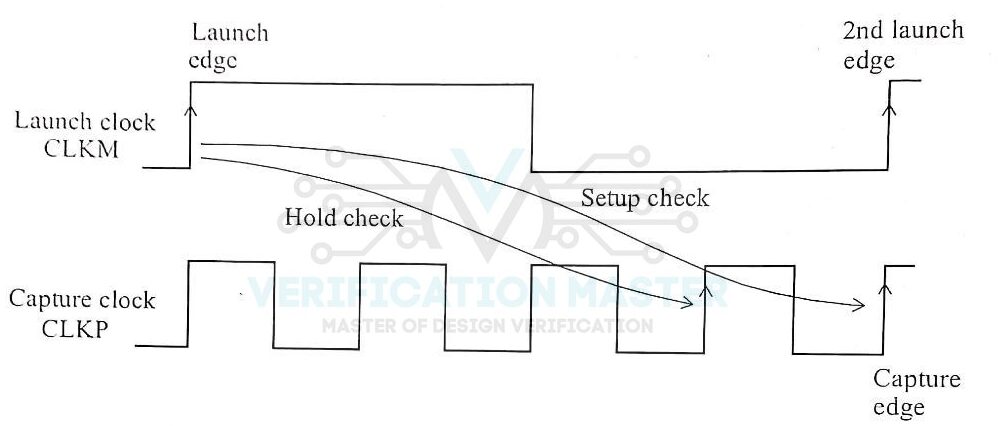

Fig. 2: Setup and Hold Check with Setup MCP

Fig. 2: Setup and Hold Check with Setup MCP

In this case, a Setup MCP of 3 is applied. So, Setup Check will take place on 4th Active Edge of Clock and Hold Check by default will take place one Clock Edge before Setup Check i.e. 3rd Active Edge of Clock.

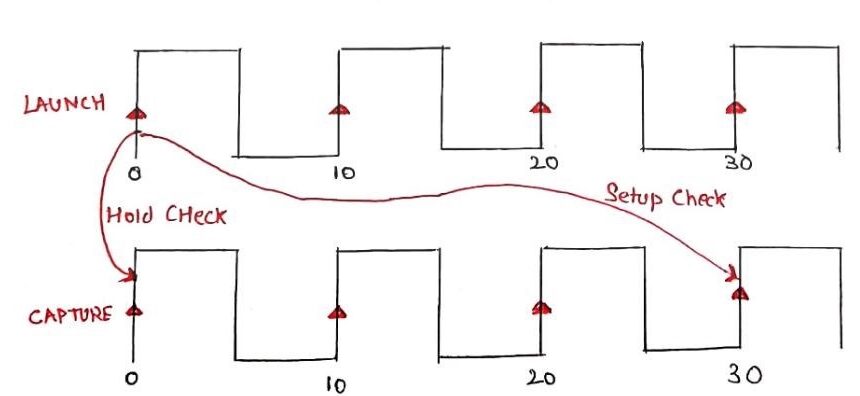

Fig. 3: Setup and Hold Check with Setup and Hold MCP

In this case, a Setup MCP of 3 is applied and a Hold MCP of 2 is applied. So, the Setup check will take place on the 4th Active Clock Edge and the Hold Check will take place on the Current Clock Edge i.e. 0ns. The reason behind applying Hold MCP is that the Hold Check always takes place on the Current Active Clock Edge.

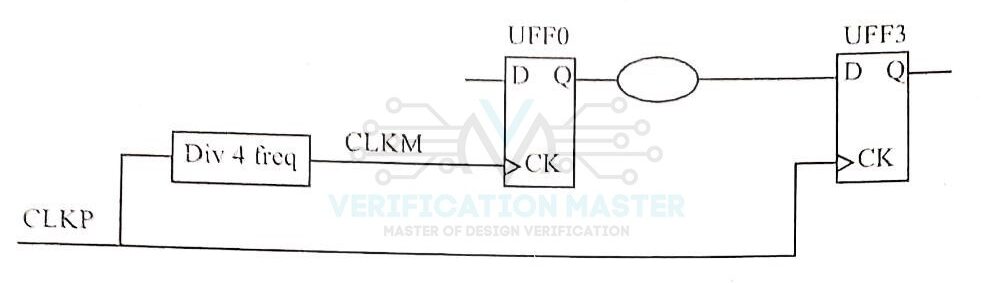

Slow to Fast Setup and Hold Check

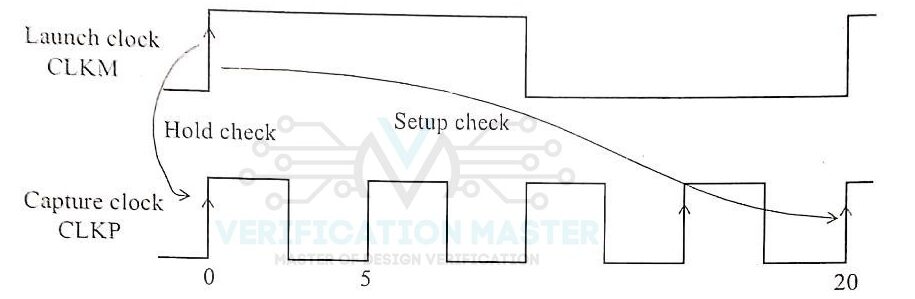

Fig. 4: Slow to Fast Setup and Hold Check

Consider the Path which goes from a Slow Clock Domain to Faster Clock Domain as shown in above Fig.4 Let us take Period of Launch Clock 20ns and Period of Capture Clock 5ns. Common Base is 20ns. So, 6 Edges will be added to get a Common Base in this case. Now, let us perform Setup and Hold Analysis for the Case.

Case 1: Default Setup and Hold Check

This is the Default Case the Setup Check is done on Next Active Edge of Capture Clock and Hold Check is performed on Current Active Edge. Refer to Fig. 5

Fig. 5: Default Setup and Hold Check

Case 2: Multicycle Constraint for Setup

Specifying Multicycle Path between the two Clock Domains will change the Edges of Setup Check and Hold Check. Below Command can be used for specifying a Multicycle Path for Setup.

set_multicycle_path 4 -setup -from [get_clocks CLKM] -to [get_clocks CLKP] -end

Here, -end specifies that the Multicycle Path constraint is applied to the Capture Clock. Refer to Fig. 6. As Hold Check is done one Edge before the Setup Check.

Fig. 6 Multicycle Constraint for Setup

Case 3: Multicycle Constraint for Hold

To ensure that the Hold Check is done on the Current Capture Clock Edge a Multicycle Path is defined for Hold that will move the Hold Checking Clock Edge back three Clock Cycles. The below command can be used to specify Multicycle Path for Hold.

set_multicycle_path 3 -hold -from [get_clocks CLKM] -to [get_clocks CLKP] -end

Using the above Command the Hold Check will be done on Current Active Clock Edge. Refer to Fig. 7

Fig. 7 Multicycle Constraint for Hold

Fast to Slow Setup and Hold Check

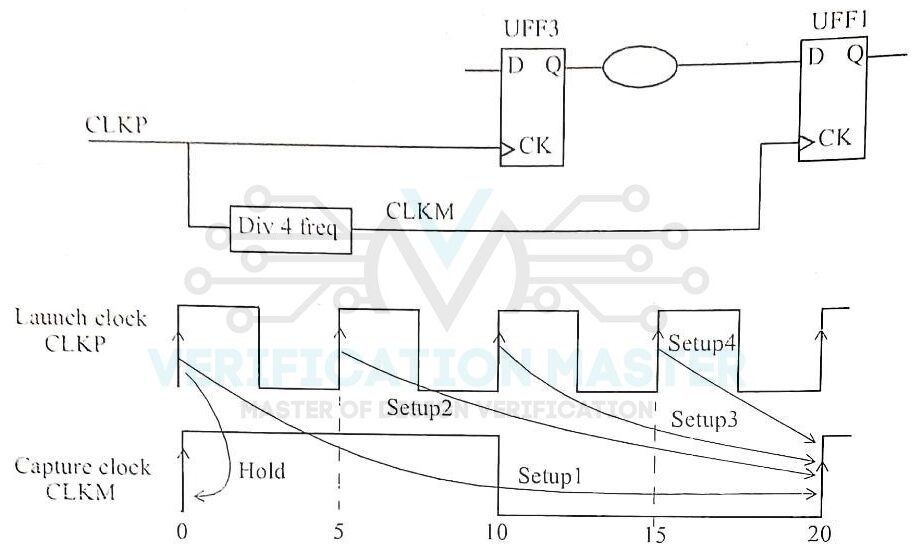

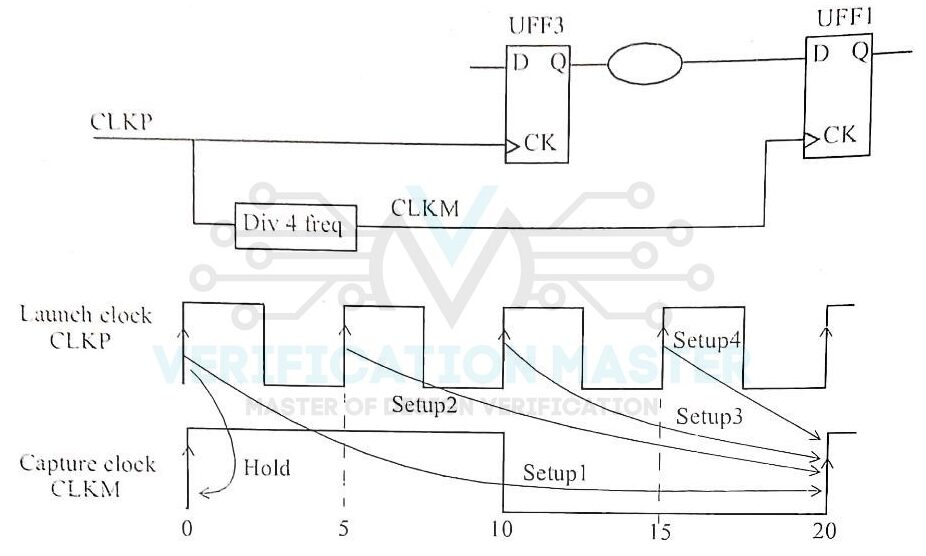

Fig. 8 Fast to Slow Setup and Hold Check

Consider the Path which goes from a Fast Clock Domain to Slower Clock Domain as shown in above Fig.8 Let us take Period of Launch Clock 5ns and Period of Capture Clock 20ns.

Case 1: Default Setup and Hold Check

There are Four Setup Checks present S1, S2, S3, and S4. But, S4 is the most pessimistic. For S4 Launch Clock Edge is at 15ns and Capture Clock Edge is at 20ns. Similarly, Four Hold Checks are present among which most Pessimistic cases are shown. The Hold Check ensures that the Data Launched at 0 should not be Captured at 0. Refer to Fig. 9

Fig. 9 Default Setup and Hold Check

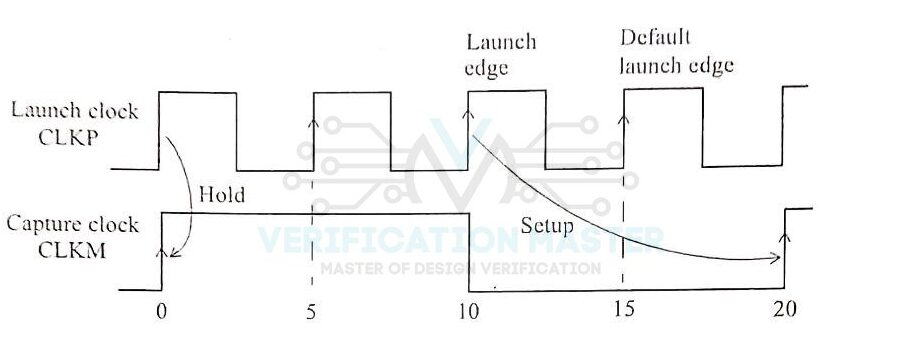

Case 2: Setup and Hold Multicycle Constraint Applied

Specifying Setup and Hold Multicycle Path between the Launch and the Capture Flop is beneficial in this case. Use the below Commands to relax the Setup Check for two Clock Cycles of Faster Clock. Refer to Fig. 10

set_multicycle_path 2 -setup -from [get_clocks CLKP] -to [get_clocks CLKM] -start set_multicycle_path 1 -hold -from [get_clocks CLKP] -to [get_clocks CLKM] -start

-start specifies that Multicycle Path Constraint is applied for Launch Clock. This Command will move Launch Edge one Edge before Default Launch Edge i.e. at 10ns instead of 15ns. The Hold Multicycle makes sure that the Capture of Data occurs at 0.

Fig. 10: Setup and Hold Multicycle Constraint Applied

So from this Blog, you can answer the below set of questions:

- What is a Multicycle Path?

- Give two scenarios of the Multicycle Path.

- How does the Setup and Hold check change on applying Setup and Hold MCP constraints? Explain with waveform.

- Explain the case of Slow to Fast CDC along with Setup Check and Hold Check.

- Explain the case of Fast to Slow CDC along with Setup Check and Hold Check.