“STATIC” in STA

STATIC refers to something independent w.r.t time in performing Timing Analysis. In Timing Analysis if you make the Analysis independent of the Input Vectors Applied (which is the only thing that can vary with time) then it is known as Static Timing Analysis.

Now the question may arise that How it is possible to perform Timing Analysis without Input Vectors and is it meaningful or not? and Is it possible to make a circuit independent of Input Vectors?

Timing analysis is a method to calculate that how much time/delay a signal will take from its start point to its endpoint or you can say that how much time a circuit takes for a certain change in input will be reflected at the output So, you can understand this by an example as in Fig.1.

Suppose you have to go to an Institute from your home and you have to calculate that how much time will it take to reach there (here home is the starting point and institute is the endpoint). So for this, you have to select a route that will take the least time and shortest path to reach there. But, how will you do this? One way is that you will go there at different times of the day and following different routes. So it will be very much difficult to cover all the possible routes and at different intervals of time and if you even cover all the possibilities then it will be a very exhaustive method to perform such analysis and such type of analysis is known as Dynamic Analysis.

So now what is the solution? You can do few things like ask your different friends who follow the same route daily, you can use Google maps to get an idea about the shortest route. So these are the two methods that can help you out so you get an idea about the shortest path and time while being at home so such type of analysis is known as Static Analysis.

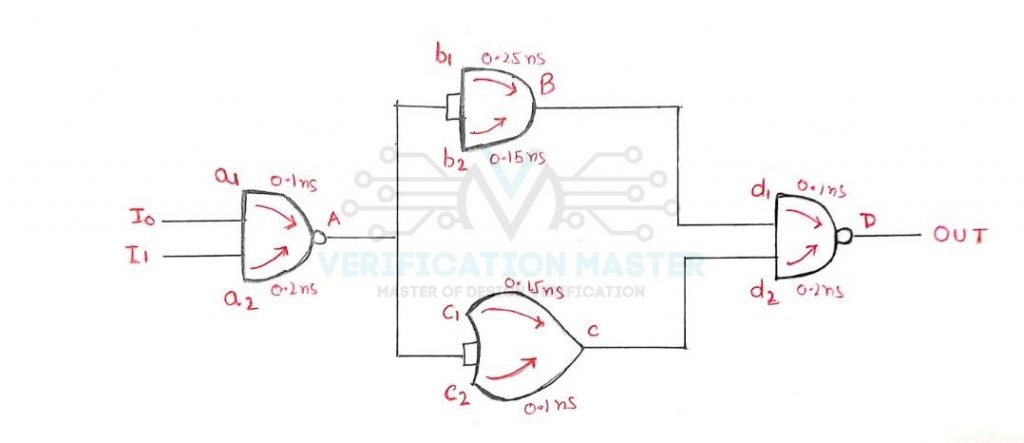

In a similar way, you have to calculate time/delay in a circuit as in Fig.2 where inputs I0 and I1 are the starting point and OUT is the endpoint. You can notice that for every Logic Gate there are two possible paths with different delay value through which a signal can travel. So timing analysis should be done in such a way that signal will travel through the shortest path that will take less time.

So, in the VLSI industry also if a circuit is tested using different input vectors then such analysis is known as “Dynamic Timing Analysis” and if a circuit is tested for timing without applying input vectors such analysis is known as “Static Timing Analysis”.

In VLSI there are different teams responsible for providing the timing data as they have already done extensive calculations and analysis to get the Delay Values of different paths in a circuit at different intervals of time considering the rising edge, falling edge, minimum delay, maximum delay, and various other parameters. The delay information you can get from different vendors who have already done many projects and are responsible for the successful fabrication of several SoC(System on Chip). The file in which timing information of different Logic Gates and Macros used in the circuit is present is called as Liberty(.lib) file. So STA is performed taking reference from those Liberty files

Static Timing Analysis (STA)

Static Timing Analysis is the method to validate a circuit design in terms of Timing. STA process checks a design for various Timing Violations and removes those Violations for the proper functioning of a chip at the required Operating Frequency.

In STA timing analysis is carried out without applying Input Vectors. The Timing information of each Standard Cell is given in Liberty File. Many checks are done in the process of STA for example Setup Check and Hold Check. Setup check verifies that the data is received from Launch Flop to Capture Flop within the given Time Period and Hold Check verifies that the Data is held for a minimum amount of time to be processed correctly and is captured correctly.

Advantages of STA

- It performs timing checks for all the possible paths of the design. So STA is a very exhaustive process.

- It is a faster and simple process for validating the timing of a design.

Disadvantages of STA

- It is not applicable for Asynchronous Designs,

- One more limitation is that it only deals with Logic ‘0’ and Logic ‘1’ values but not with ‘X’ which is an unknown value

- STA does not deal with Analog circuits.

Dynamic Timing Analysis (DTA)

On the other hand, DTA is a process in which Input Vectors are applied and simulation is done. Results of DTA are better than STA if it covers all the possible Input Vectors. As there can be millions of Input Vectors combinations so it is a very time-consuming process and also it very difficult to cover all the possible combinations of Input Vectors. So this is the reason why DTA is not preferred for Timing Analysis.

STA vs DTA

| STA | DTA |

| Input Vectors are not Required | Input Vectors are Required |

| Less Time Consuming | More Time Consuming |

| Less Accurate | More Accurate |

| Exhaustive Process | Non-Exhaustive Process |

| Cannot Detect Error Related to Logical Operation | Check Functionality so detect Logical Error |

When to use STA and when to use DTA?

STA can only be performed for Synchronous Designs but not for Asynchronous Designs. DTA can be used for both Synchronous and Asynchronous Designs. DTA is also advantageous for designs where Multiple Clock Domains are present. As the number of test vectors increases, the accuracy of DTA increases. But, note that DTA and STA are not alternatives to each other.

Spice Simulation

Spice simulation is used to carry out device level Timing Analysis. To verify the electrical properties of full custom designs Spice simulation is necessary. These calculations are done based on mathematical equations that represent the electrical properties of the devices. Model files store the information about the material and few electrical properties of the devices For example Electron Density, Threshold Voltage of MOS, etc. Spice simulated data is stored in technology libraries and used for carrying out STA. The simulation is most accurate as compared to other forms of simulation. It is also a difficult task because Spice codes are written manually. Pathmill from Synopsys is used to carry out transistor-level STA.

- So from this blog below questions can be answered-:

- What does “STATIC” mean in STA?

- Give a Real Life Example of STA.

- What is Dynamic Analysis?

- Compare between Static Analysis and Dynamic Analysis.

- What is Static Timing Analysis?

- What is Dynamic Timing Analysis?

- Difference between STA and DTA

- When to use STA and When to use DTA?