As we learned from the previous blog about the different types of modeling, we already know about behavioural modeling.

In this blog we will study that in more detail.

Structured Procedures

Verilog has two structured process statements: always and initial. These are the two most fundamental propositions in behavioural modelling.

All additional behavioural statements are only permitted to occur within these structured process statements. We studied this in the previous blog, so we will learn this in short.

The statements initial and always define independent processes, which implies that the statements in one process operate independently. Both sorts of processes are made up of procedural statements and begin as soon as the simulator is launched.

Initial statement

An initial block is made up of all statements that follow an initial statement. An initial block begins at time 0, executes precisely once throughout a simulation, and then stops.

If there are many beginning blocks, each one begins execution at time 0. Each block completes execution independently of the others.

Several behavioural statements must be grouped together. The terms “begin” and “end” are commonly used. If there is only one behavioural statement, no grouping is necessary.

This is analogous to the begin-end blocks in Pascal programming or the /grouping in C programming.

module stimulus;

reg a, b, m;

initial

m= 1’b0; // single statement

initial

begin

#10 a=1’b1; // multiple statement

#25 b =1’b0;

end

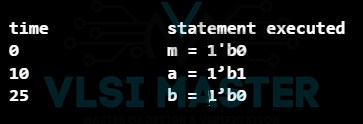

The preceding example shows both a single initial statement and multiple statements, whereas multiple sentences are not required to be grouped.

Fig 1: Output

Both of the initial statements are executed simultaneously at time 0. If delays are stated before a statement, then after that amount of time units after the present simulation time.

Typically, the initial block is used for initialization, monitoring, waveforms, and other processes that must be completed just once during the simulation run.

Always statement

An always block is made up of all the behavioural statements included within an always statement. The always statement begins at time 0 and loops through the statements in the always block indefinitely.

This statement is used to represent a continuous block of activity in a digital circuit. A clock generator module, for example, toggles the clock signal every half cycle. The clock generator in actual circuits is active from time 0 to as long as the circuit is switched on.

module clock_gen;

reg clock;

//clock at t=0

Initials

clock = 1’b0;

//clock every half-cycle t=20

always

#10 clock = ~clock;

initial

#1000 $finish;

endmodule

The always statement in above Example begins at time 0 and performs the statement clock-to-clock every 10 time units. It is important to note that the clock must be initialised within a separate begin statement.

If we place the clock initialization within the always block, the clock will be initialised each time the always is entered. Furthermore, the simulation must be terminated within an initial statement.

If no $stop or $finish statement is used to terminate the simulation, the clock generator will continue indefinitely.

C programmers may see the always block as analogous to an endless loop. However, hardware designers tend to see it as a continually recurring action in a digital circuit that begins when the power is turned on.

Only power off ($finish) or an interrupt ($stop) will terminate the activity.

Procedural assignment

Procedural assignments update values of regular, integer, real, or time variables. The value placed on a variable will remain unchanged until another procedural assignment updates the variable with a different value.

These are unlike continuous assignments discussed in previous blog, Dataflow Modeling, where one assignment statement can cause the value of the right-hand-side expression to be continuously placed on the left-hand-side net.

The syntax for the simplest form of procedural assignment is shown below.

<assignment>

: : = <1value> = <expression>

<1value> can be any of the values listed below.

- A reg, integer, real, or time register variable or a memory element

- a subset of these variables

- a portion of these variables

- a concatenation of any of the above.

On the right hand side, you can be any expression that evaluates to a value. There are two types of procedural assignment, explained below.

Blocking statement

In a sequential block, blocking assignment statements are performed in the order given. A blocking assignment will not block statements in a parallel block from being executed.

Nonblocking statement

Nonblocking assignments allow assignments to be scheduled without interfering with the execution of the statements that follow in a sequential block.

Nonblocking assignments are specified using the <= operator. A less_than_equal_to is the same symbol as the relational operator.

In an expression, the operator <= is understood as a relational operator, and in the context of a nonblocking assignment, it is interpreted as an assignment operator.

Application

always @ (posedge clock)

begin

reg1 <= #1 a;

reg2 <= @(negedge clock) b^c;

reg3 <= #1 reg1; // previous value of reg1

end

For nonblocking assignments, the following process occurs at each positive edge of the clock.

1. At the positive edge of the clock, each right-hand-side variable, a, b, c, and reg1, is read.

2. The write operation to the left-hand-side variables is planned to be conducted at the time indicated in each assignment by the intra-assignment delay.

3. The write operation is carried out in the time steps specified.

After reading this blog, you will be confident in your understanding of the many sorts of statements in behavioural modelling.

So let’s summarise the entire blog with some questions that you can simply answer and that will also help you learn in a more easy method.

- What are the many forms of behavioural modelling?

- What are the many forms of structured procedures?

- What is the distinction between the first statement and the always statement?

- What exactly is a procedural assignment?

- Is there a difference between blocking and nonblocking statements?

- What are nonblocking statements used for?