Before starting placement it is better to do some analysis and checks on design/tool settings. This helps in reducing iterations.

- Check for missing or extra placement and routing blockages(Hard/Soft/Partial).

Try using partial blockages mostly as they take some ratio of inverters/buffers while doing optimization. Hard blockages don’t allow any optimization cells, so it would be difficult to achieve timing for paths of that particular area.

- Do not touch cells are to be identified before performing any pre-placement or placement steps/optimizing techniques.

Can refer what are don’t touch cells in previous topic.

- Check PG connection for all cells in design.

Make a logical connection of pg pins/ports with pg nets. This is done in Poweplan stage. But make sure they are logically connected.

check_pg_connectivity

- Make sure the clock is set ideal.

What is Ideal Clock?

The clock with Zero Delay is generally an Ideal clock. The clock is synthesized later in the design. So, clocks are defined ideally. If High Fan-out Net Synthesis(HFNS) is done on clock nets, clock constraints like Skew, Clock Buffer are not used in this stage and the clock tree will be messed up.

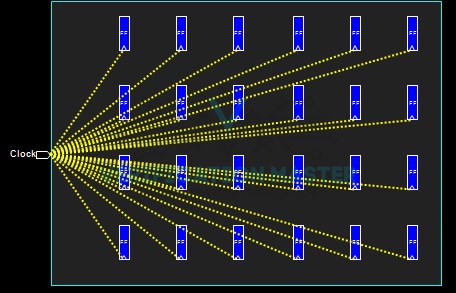

Ideal clock

Here in the above fig, the clock is transmitted ideally for complete design which means all sequential cells receive the clock at the same time without any timing difference. But this is practically not possible. So this clock is synthesized in the later CTS stage.

set_ideal_clock or set_dont_touch commands on the clock signal.

- Make High fanout nets as Non-Ideal.

As we perform High Fanout Net Synthesis(HFNS) in the placement stage, we should make these nets non-ideal so that tool can synthesize them.

- In SDC Scan, Enable, Reset are ideal. Make them non-ideal in the placement stage.

Because HFNS is performed on Scan, Enable and Reset signals in the placement stage. If they are ideal tool doesn’t touch or synthesize them.

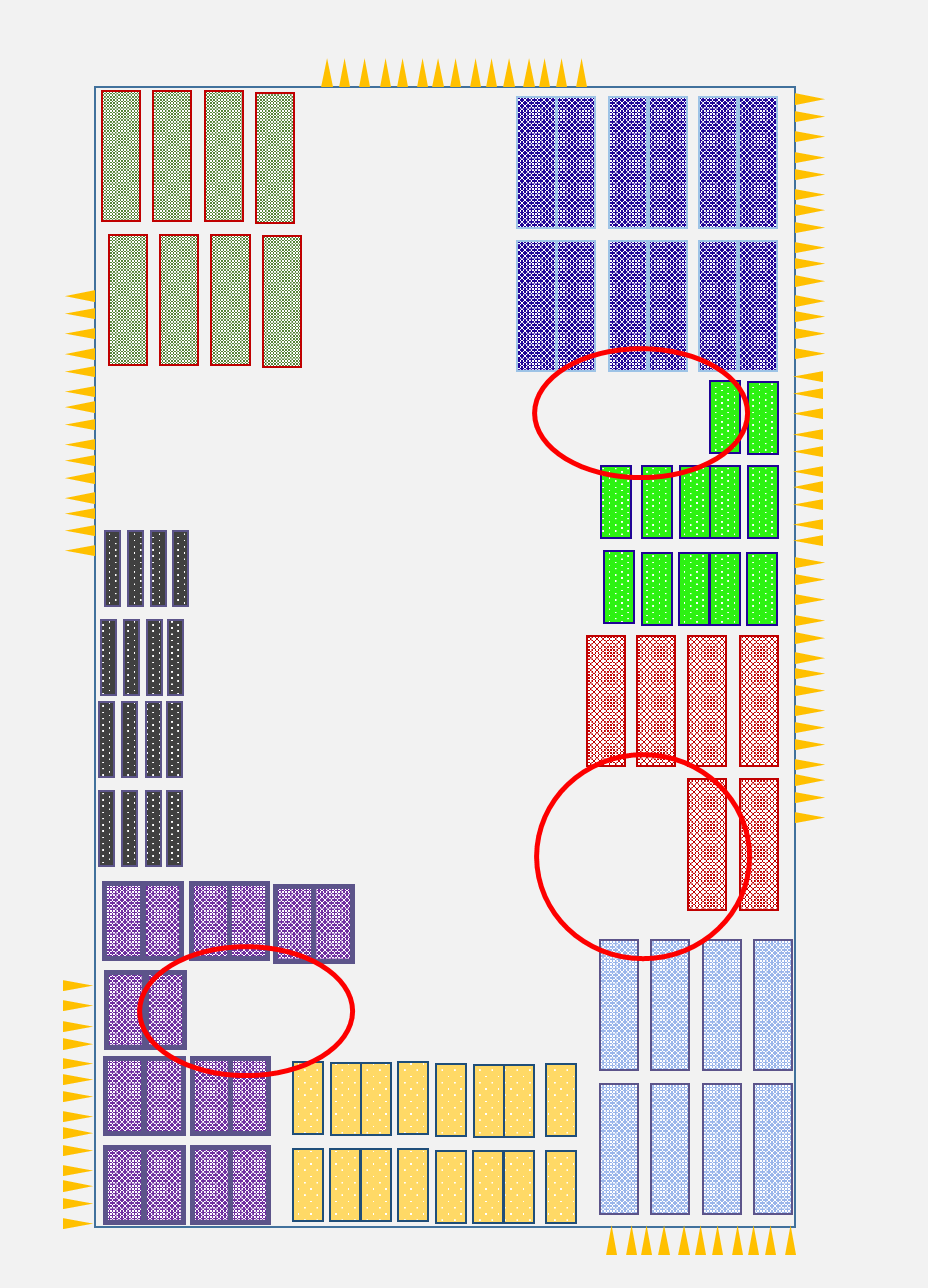

- Avoid Notches in the design.

The non-uniform shape formed in the design due to improper placement of Macros in the core. This will affect the timing of standard cells which are sitting in this notched area due to bad routing of nets( causing detour of nets and increasing the net length).

Notches